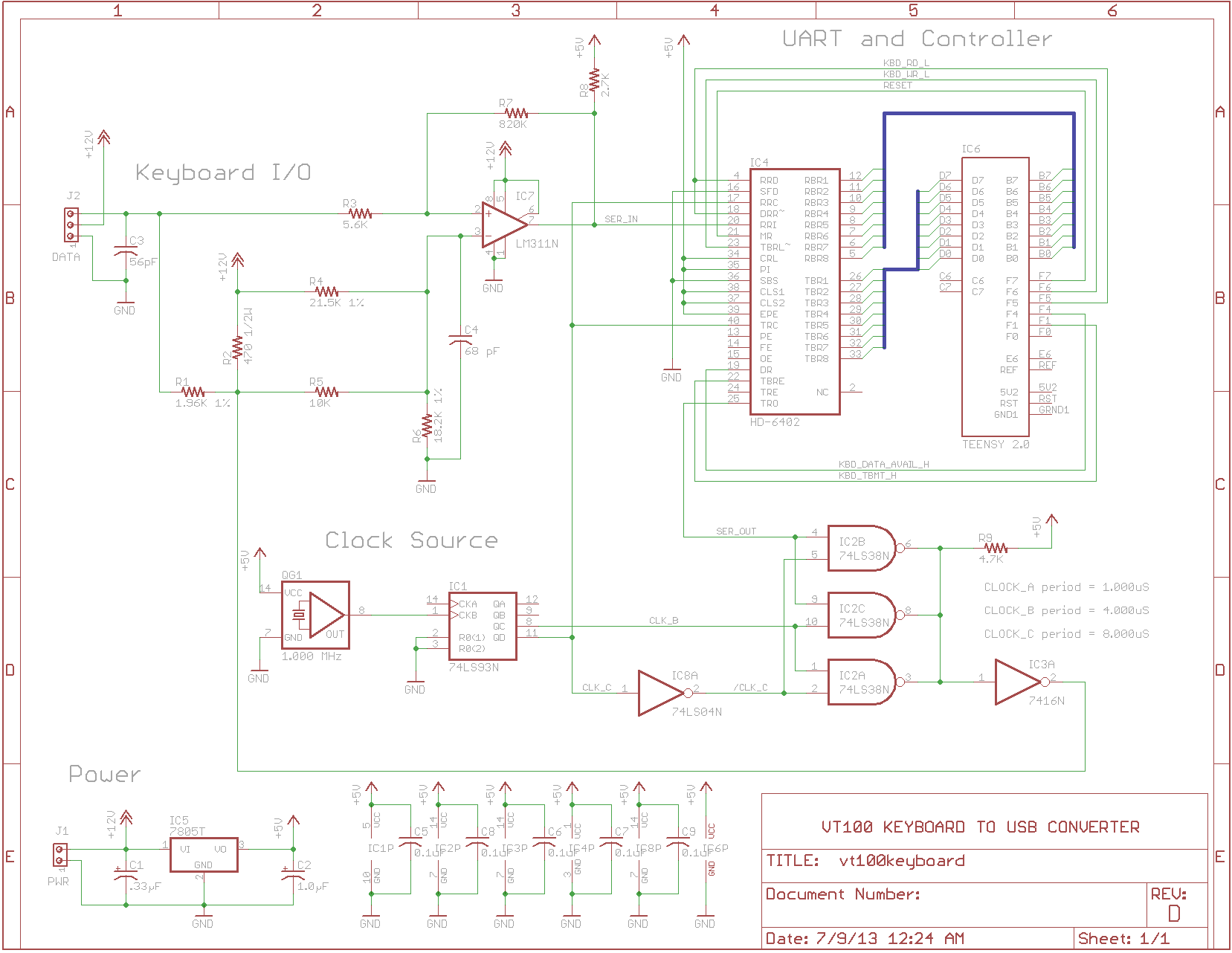

Just a quick note tonight about a hack I tried that failed. But first, here’s the latest revision of my schematic.

If you compare it to the older schematic there are a few small changes. The one I’d like to write about is the addition of IC8, a 74LS04 inverter that sits between the 74LS93 and the 74LS38 in the “Clock Source” section. It inverts the square wave with the 8 uS period. If you go back and look at the original DEC schematic, you’ll see they used one there, too. Silly me, I thought I could get away without it. But no, it turns out that UART is clocked on the rising edge, but the PWM encoded data is clocked on the falling edge. It’s a critical logic gate, otherwise the data get out of sync by half a period.

Anyway, I thought I would get clever. I reasoned that the 7416 is a perfectly usable inverter, and since the circuit already uses a 7416 elsewhere, I figured I could steal one of its spare gates as the clock inverter. It would need a pull-up resistor because it’s an open collector driver, but so what? Resistors are cheap! But mainly, I just didn’t want to have to add yet another IC, especially since I’d only be using one logic gate on it. Makes sense, right?

So I tried it, and it failed miserably. It almost worked, but it added a glitch to the clock output, a little spike in each period that shouldn’t have been there. So, grumbling to myself, I tried out a 74LS04 instead. This time, it was flawless. It worked perfectly. So much for my clever plan to save an IC.

Anyway, here’s what I think happened.

The 7416 is original, old-school TTL technology. None of this fancy

newfangled low-power Schottky stuff for us, no sir! But that means it has

a slower switching speed. Not by much, mind you, but it’s my hypothesis

that the slower switching speed caused the CLK_C output to lag behind

the CLK_B output just enough to introduce that little spike.

A glance at the datasheets reinforces that hypothesis. The High-to-Low switching speed of the 74LS04 is 4 nS minimum, 15 nS maximum. The High-to-Low switching speed of the 7416, on the other hand, is 15 nS typical, 23 nS maximum.

Teeny tiny itty-bity numbers. Unfathomably small to a dunderhead like me. But apparently big enough to cause a timing problem. Neat! I bet the DEC engineers 35 years ago tried the same thing and came to the same conclusion.

Comments